用于先进技术节点CMOSIC的新结构晶体管

《国家科学评论》杂志发表的一篇综述总结了中国科学院微电子研究所尹华祥教授领导的团队的研究。他们系统回顾了硅基金属氧化物半导体场效应晶体管(MOSFET)的发展历史,包括理论更新、新材料引入、关键工艺突破,特别是器件结构创新对先进集成电路发展的影响。IC)在过去的二十年里。

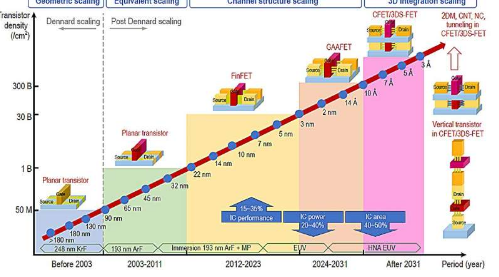

硅基晶体管的结构将从鳍式场效应晶体管(FinFET)更改为3nm节点的尖端堆叠式纳米片/纳米线环栅FET(GAAFET)。因此,他们介绍了最新的GAAFET集成工艺方法以及研究机构和IC行业的最新技术进展。

此外,详细说明了制造GAAFET的关键挑战,包括高质量GeSi/Si超晶格周期性外延、沟道释放、内部间隔模块、SD选择性外延缺陷、寄生子鳍沟道泄漏、HKMG填充、低孔(100)方向的迁移率、高电压(HV)和输入/输出(IO)集成以及交流操作期间的高寄生电容。作者还介绍了GAA器件的一些创新,例如ForksheetFET、TreeFET、FishboneFET和CombFET。

除了GAAFET之外,CFET(也称为3D堆叠FET(3DS-FET))也显示出向1nm节点扩展的前景。作者介绍了两种CFET集成工艺方法:顺序CFET和单片CFET。他们分析了这两种CFET结构之间的差异、各自的优势以及制造工艺中的挑战。

此外,顶层采用新型沟道材料,包括具有低温加工特性的CNT、2DM和AOS,正成为未来3D堆叠技术的趋势。除了器件结构和工艺突破之外,CFET还需要完整的DTCO或STCO来构建晶体管、电路甚至各个级别的系统,以获得更高的PPA增益。

除了水平和横向电导沟道外,还总结了垂直GAAFET(VGAAFET)的新路径,包括用于3DS-FET的垂直器件W.和WO自对准栅极。不断减小接触栅间距(CGP)、SDC和SRAM单元面积有很大的优势。此外,VGAAFET还为动态RAM(DRAM)和NOR型内存应用中的3D集成提供了新的机会。

最后,他们总结了主流IC中垂直晶体管3D堆叠应用需要解决的关键挑战,例如原子级的精确工艺控制、令人难以置信的散热以及高速电路运行过程中寄生电容/电阻的增大。行业。

他们还提供了有关将晶体管3D堆叠与创新单片3D和系统中的隧道、负电容和量子器件等新理论晶体管集成的未来开发路径的见解。该审查对3nm及以上节点的先进IC制造、建模和设计领域具有重要指导意义。

免责声明:本文由用户上传,与本网站立场无关。财经信息仅供读者参考,并不构成投资建议。投资者据此操作,风险自担。 如有侵权请联系删除!

-

在众多紧凑型性能车中,大众高尔夫GTI始终以其独特的驾驶乐趣和经典形象占据着重要地位。对于预算有限但又追求...浏览全文>>

-

2022款的大众蔚揽以其优雅的设计和出色的性能在市场上占据了一席之地。对于预算在20-30万元之间的消费者来说,...浏览全文>>

-

池州长安启源E07作为一款备受关注的新能源SUV,在市场上拥有较高的关注度。这款车型凭借其时尚的设计和丰富的...浏览全文>>

-

近年来,随着汽车市场的竞争愈发激烈,各大品牌纷纷推出优惠政策以吸引消费者。作为国内知名汽车品牌之一,蚌...浏览全文>>

-

菱势汽车的菱势电卡是一款新能源物流车,如果您想预约试驾这款车型,以下是可能的流程及注意事项:预约试驾流...浏览全文>>

-

奥迪e-tron GT是一款融合了豪华与科技的电动跑车,如果您对这款车型感兴趣并希望进行试驾体验,可以通过以下...浏览全文>>

-

试驾五菱扬光是一次非常有趣的体验。以下是从咨询到试驾的完整体验过程:咨询阶段1 信息获取:首先通过官方...浏览全文>>

-

在试驾丰田bZ3C时,享受4S店专业服务的关键在于提前做好准备,并充分利用4S店提供的各项资源。以下是一些具体...浏览全文>>

-

近年来,新能源汽车市场蓬勃发展,各大品牌纷纷推出全新车型以满足消费者需求。作为大众汽车旗下备受关注的新...浏览全文>>

-

作为一款备受关注的新能源车型,2022款亳州迈腾GTE在市场上的表现一直引人注目。近期,其最低落地价已降至18 ...浏览全文>>

- 蚌埠揽巡最新价格2024款走势,市场优惠力度持续加大

- 亳州迈腾GTE多少钱 2022款落地价走势,近一个月最低售价18.79万起,性价比凸显

- 安庆探影多少钱?价格解读

- 天津滨海高尔夫GTI最新价格2025款,各车型售价大公开,性价比爆棚

- 试驾奕泽IZOA,感受豪华与科技的完美融合

- 五菱E5试驾预约操作指南

- ARCFOX极狐极狐 阿尔法S6试驾有哪些途径

- 奔腾T55预约试驾有哪些途径

- 东风风度帕拉丁试驾,开启完美驾驭之旅

- 试驾腾势N7,一键搞定,开启豪华驾驶之旅

- 开沃D10多少钱?经销商报价及市场优惠情况

- 飞度新款价格2025款多少钱?如何挑选性价比高的车

- 东莞途锐 2025新款价格全解买车必看

- 试驾东风小康EC36 II的流程及注意事项

- 北京BJ30预约试驾预约流程

- 奥迪A6(进口)试驾预约,从咨询到试驾的完整体验

- 东风本田M-NV试驾全攻略

- 欧拉芭蕾猫落地价全解,买车必看的省钱秘籍

- 龙耀8L新车报价2022款,各配置车型售价全解析

- 沃尔沃S60新能源多少钱 2024款落地价实惠,配置丰富,不容错过